微机期末复习之知识总结

第一章

QUS

简答

- 处理器字长:处理器单位时间内可以处理的二进制位数。

- 总线信号分为哪三种:数据总线、地址总线、控制总线

- 取指译码执行周期是指什么:从主存储器读取指令、翻译指令代码的功能、执行指令所需要的操作。

判断

- IA-64结构是IA-32结构的64位扩展,也就是Intel64 结构? ×

- 微机主存只要使用RAM芯片就足够了? ×

大题

- 什么是通用微处理器、单片机(微控制器)、DSP芯片、嵌入式系统?

- 通用微处理器:适合较广领域的微处理器芯片,例如装在笔记本上的。

- 单片机:是指通常用于控制领域的微处理器芯片,其内部除了CPU外还集成了计算机的主要部件,只需要配上少量外部电路和设备就可以工作。

- DSP芯片:数字信号处理器,也是一种微控制器,其更加适合处理高速的数字信号,内部集成有告诉的乘法器,能够进行乘法和加法运算。

- 嵌入式系统:利用微控制器、数字信号处理器或者通用微处理器结核病具体应用构成的控制系统。

- 区分:类路径、绝对路径、相对路径、当前目录。

- 路径:操作系统以目录的形式管理磁盘上的文件,文件所在的分区和目录就是该文件的路径。

- 绝对路径:从根目录到文件所在的目录的完整的路径称为绝对路径,是保证文件唯一性的指示方法。

- 相对路径:从系统当前目录到文件所在目录的路径称为相对路径。

- 当前目录:用户当前所在的目录。

- 冯诺依曼计算机的基本设计思想是什么?

- 采用二进制表示数据和指令。指令由操作码和地址吗组成。

- 将程序和数据存放在存储器中,计算机在工作时从存储器中取出指令加以执行,自动完成计算任务。

- 指令的执行是顺序的,即按照指令在存储器中的存放顺序执行、程序分支由转移指令实现。

- 计算机由存储器、运算器、控制器、输入输出设备组成。

- 计算机系统的层次。

最长层是用户层。

第五层是高级语言层。

第四层是汇编语言层

第三层是操作系统层

第二层是机器语言层

第一层是控制层

第零层是数字电路层

第二章

指令执行过程

- 取指:指令处理单元从主存中将指令取出并通过总线传输到处理器内部的指令寄存器中。

- 译码:指令处理单元通过指令译码电路获得该指令的功能。

- 执行:指令的处理单元的时序和控制逻辑按照一定的时间顺序接收响应的信号,完成至指令所要求的额操作。

存储模型

- 平展存储模型

- 段式存储模型

- 实地址存储模型

16位模拟DOS平台开发环境代码框架

1 | include io16.inc |

QUS

简答题

- 8086取指为什么可以被称为指令预取?

8086分成总线接口单元和指令执行单元,可以独立操作。在执行单元执行一条指令的同时,总线接口单元可以读取下一条指令,等到执行的时候不用再进行取指了,所以称为预取。

- 标志寄存器主要保存哪一些方面的信息?

指令执行结果和控制指令的执行形式。

- 除外设外的数据寻址方式有三类,分别为:立即数寻址、寄存器寻址、存储器寻址。

- 说明以下指令中源操作数的寻址方式。 VARD是一个双子变量。

指令 寻址方式 mov edx,1234h 立即数 mov edx,VARD 直接 mov edx,ebx 寄存器 mov edx,[ebx] 寄存器间接 mov edx,[evx+1234h] 寄存器相对 mov edx,VARD[ebx] 寄存器相对 mov edx,[ebx+edi] 基址变址 mov edx,[ebx+edi+1234h] 相对基址变址 mov edx,VARD[esi+edi] 相对基址变址 mov edx,[ebp*4] 带比例寻址

第三章 第四章 汇编基础知识

第五章 微机总线

- 微机以总线作为信息传输的公共通道。

- 总线结构的特点

- 通过总线互相连接,实现数据传输。

- 组态灵活,易于扩展。

- 总线类型

- 芯片总线:在大规模集成电路内部进行芯片级互连。

- 内总线:模板级互连

- 外总线:设备级互连

- 总线操作

- 总线请求和仲裁:使用总线的主模块提出申请,总线仲裁机制确定把总线分配给请求模块。

- 寻址:主模块发出将要访问的从模块地址信息以及有关命令,启动从模块。

- 数据传送:源模块发出数据,经数据总线传送到目标模块。

- 结束:数据、地址、状态、命令信息均从总线上撤除,让出总线。

- 同步方式

- 同步时序:总线操作过程由公用的总线时钟信号控制,适合速度相当的设备。

- 总线的操作需要握手联络应答信号控制,开始伴有启动、选通或者读写信号。

- 传输的结束有一个确认信号,进行应答。

- 操作周期可变,适应速度相差很大的设备。

- 总线的性能指标

- 总线宽度:总线能够同时传送的数据位数。

- 总线频率:总线信号的时钟频率。

- 总线带宽:单位时间内传送的数据量。

- 总线分类:地址总线、数据总线、控制总线。

QUS

简答题

- 为什么称处理器的数据总线是双向的?

数据总线承担着处理器和存储器、外设之间的数据交换、既可以输入也可以输出。

- 具有三态能力的引脚输出高阻意味着什么?

相当于连接了一个阻抗很高的外部器件,信号无法正常输出,即放弃对于该引脚的额控制,断开其连接。

- 总线时钟周期中的等待状态意味着什么?

处理器检测到存储器或者IO端口速度太慢,不能按照基本的总线周期进行数据交换,插入一个等待状态Tw,保持总线信号不变。

- 什么是猝发传送?

处理器只提供首地址、但可以从后续连续地存储单元中读写多个数据。

- 总线周期:

总线请求和仲裁、寻址、数据传送、结束。

- 处理器基本的总线操作:

存储器读 存储器写 IO读 IO写

大题

- 8086处理器输入控制信号有RESET,HOLD,NMI,INTR,他们的具体含义是什么?当他们有效时,8086CPU将做出什么反应。

- RESET:复位出入信号,高电平有效。有效时,迫使处理器回到其初始状态,转为无效时,处理器继续工作。

- HOLD:总线请求,高电平有效。有效时,表示其他总线主控设备向处理器申请使用原来由处理器控制的总线。

- NMI:不可屏蔽中断请求,是一个利用上升沿有效的输入信号。有效时表示外界正在向CPU申请不可屏蔽中断。

- INTR:可屏蔽中断请求,高电平有效,有效时表示中断请求设备向CPU发出可屏蔽中断请求。

- 区分概念:指令周期,总线周期(机器周期),时钟周期,T状态。

- 指令周期:一条指令从取指译码到执行完成的过程。

- 总线周期(机器周期):有数据交换的总线操作。

- 始终周期:处理器的基本工作节拍,由时钟信号产生,一个高电平一个低电平位一个周期。

- 完成特定操作的一个时钟周期。

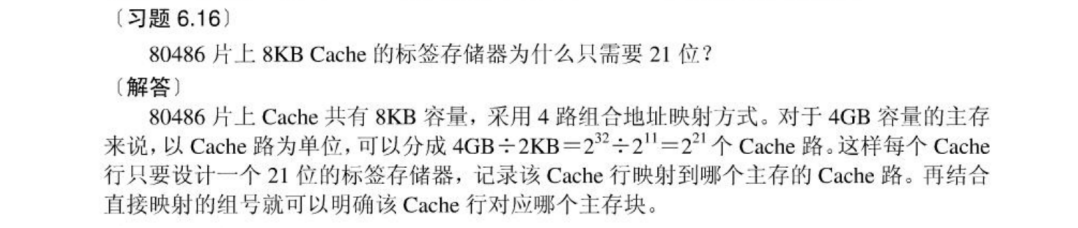

- T1:总线周期的第一个时钟周期主要用于输出存储器或者IO地址。

- T2:输出读/写控制信号。

- T3:锁存地址、处理器提供的控制信号和数据再总线上继续维持有效,且T3时钟的前沿(下降沿)对READY引脚进行检测。若有效则进入T4。

- T4:总线周期的最后一个时钟周期,处理器和存储器或者I/O端口进行数据传输直到完成,并为下一个时钟周期做好准备。

- Tw:等待状态。T3时READY信号无效时,插入Tw,延续T3的状态,维持不变。

- 请解释8086(最小组态)以下引脚的含义:CLK, A19/S6~A16/S3,AD15~AD0, ALE,M/$\overline{\text{IO}}$, $\overline{\text{RD}}$, $\overline{\text{WR}}$。并画出其在一个具有等待状态的读总线周期的波形示意。

- CLK:时钟输入。其频率就是处理器工作的频率。

- A19/S6~A16/S3:地址/状态时分复用引脚,在访问存储器的第一个时钟周期输出高四位地址A19~A16,在访问外设的第一个时钟周期输出低电平无效。其余时间输出状态信号S6~S3。

- AD15~AD0:地址/数据时分复用引脚,用作地址线时是单项输出,用作数据线时时双向。

- ALE:地址锁存允许,是一个三态、输出、高电平有效的信号。有效时,表示复用引脚A19/S6~A16/S3,AD15~AD0正在传输地址信号。

- M/$\overline{\text{IO}}$:访问存储器或者IO,高电平为存储器(A19~A0),20位,低电平时为(A15~A0)16位IO端口。

- $\overline{\text{RD}}$:读控制,低电平有效,表示正在读(存储器或者IO)

- $\overline{\text{WR}}$:写控制,低电平有效,表示正在写(存储器或者IO)

- 时序

- 同步时序:总线操作的各个过程由共用的总线时钟信号控制。

- 半同步时序:总线操作的各个过程由共用的总线时钟信号控制,但是慢的设备可以通过等待信号让快设备等待。

- 异步时序:总线操作需要握手联络应答信号控制,总线时钟信号可有可无。

第六章 存储系统

- ram

| RAM类型 | 组成单元 | 速度 | 集成度 | 应用 |

|---|---|---|---|---|

| SRAM | 触发器 | 快 | 低 | 小容量系统 |

| DRAM | 单个MOS管 | 慢 | 高 | 大容量系统 |

| NVRAM | 触发器 | 快 | 低 | 有后备电池 |

- cache地址映射方式

- 直接映射:将一个主存块存储到唯一的cache行

- 全相联映射:将一个贮存快吧存储到任意一个cache行

- 组相联映射:将一个主存块存储到唯一一个cache组的任意一行。

- 页表

- 不详细说了,在os里面讲过

QUS

简答题

- 什么时高速命中,什么时告诉缺失(未命中)?

- Cache中复制这主存中的部分内容。让处理器试图读取某一个字的时候,Cache控制器会首先检查Cache中是否已经包含这个字,若包含,则处理器直接读取Cache的内容,称为高速命中,反之,称为高速缺失。

- 什么时Cache的地址映射?

- 主存块和Cache行组之间的映射关系称为地址映射。分为直接映射,全相联映射,组相联映射。

- Cache写入策略用于解决什么问题?

- 用于解决写入Cache时引起主存和Cache不一致的问题。

- 存储器的存取时间和存取周期有什么区别?

- 存储时间表示读写命令发出到数据传输完成所需要的时间,存储周期表示两次存储器访问所允许的最小时间间隔。

- DRAM芯片怎么既有行地址又有列地址?

- DRAM时分复用地址线,先传送行地址再传送列地址。

- 译码分类

- 全译码:使用全部地址总线进行译码,地址唯一,一个存储单元对应一个存储器地址。

- 部分译码:只是用部分地址总线进行译码,每有一个没有使用的地址信号就会有两种不同的编码指向同一个存储单元,出现地址重复。

- 区分以下主存名称的含义。

- 常规主存:再1MB空间中的第640KB系统RAM区称为常规主存或者基本主存。

- 扩展主存:IA-32处理器在1MB之后的主存空间称为扩展主存。

- 扩充主存:处理器不可以直接访问,利用体交换技术实现访问。

- 上位主存区UMA:在常规主存区后384K(A0000H~FFFFFH)称为UMA

- 上位主存块UMB:UMA没有使用的部分称为UMB

- 高端主存区HMA:1MB之上的64KB.

- 影子主存:PC机启动后可以将ROM-BIOS映射到RAM中,这部分用作RAM-BIOS的主存称为RAM,只读。

判断题

- 部分译码可以简化译码电路,且不会减少可用的存储空间。 ×

- DRAM芯片上的所有单元同时刷新一次。×

- 存储系统的刷新地址提供给所有的DRAM芯片。 √

填空题

- 对一个存储器芯片进行片选译码时,有一个高位系统地址信号没有参加译码,则该芯片扽每一个存储单元占有几个存储器地址? ANS:2,2^1=2

- 段描述符为0000B98200002000H,则段基地址为:00820000H ,段界限为:02000

- 段描述符的结构

| 位 | 作用 |

|---|---|

| 高32位 | |

| 31-24 | 段基址31-24 |

| 23 | G |

| 22 | D/B |

| 21 | L |

| 20 | AVL |

| 19-16 | 段界限19-16 |

| 15 | P |

| 14-13 | DPL |

| 12 | S |

| 11-8 | TYPE |

| 7-0 | 段基址23-16 |

| 低32位 | |

| 31-16 | 段基址15-0 |

| 15-0 | 段界限15-0 |

大题

第七章 输入输出接口

I/O接口概述:

微机的外设多种多样,工作原理、驱动方式、信息格式、工作速度千差万别,他们不可以直接和cpu相连接,必须通过中间电路(I/O)接口电路与系统连接。I/O接口就是位于基本系统和外设之间实现两者数据交换的控制电路。其基本功能有数据缓冲和信号变换。主机和外设输送数据的方式

- 无条件传送

- 查询

- 中断

- DMA

- 专门的额IO处理机

8259A的中断处理流程

当某个外设发出一个中断信号后,由于主板已经把信号通路指向了8259A芯片的某个IRQ接口,所以该中断信号会被送入8259A。8259A先检查IMR寄存器是否屏蔽了来自该IRQ接口的中断信号,该为为1表示被屏蔽了。

将中断信号送入IRR寄存器,将该IRQ接口所在的IRR寄存器对应的位置1.

PR从IRR寄存器中挑选一个优先级最大的一个中断(IRQ接口号最低的)。

通过INT接口向CPU发送INTR信号。

CPU完成一条指令后,通过自己的INTA接口向8259A的INTA接口发送中断响应信号。

8259A收到CPU的中断响应信号后,将刚刚挑选出的优先级最大的中断在ISR寄存器中对应的位置1,表示正在处理当前中断,同时在IRR中该中断位置0。

CPU再次发送INTA信号,要求获取中断向量号。如果EIO被设置为自动的话,则8259A自动将ISR对应位置0,表示中断结束,否则需要手动发送EOI信号

8259A向CPU发送中断向量号。此时如果来了一个优先级更高的中断,则将该中断替换上去,将被替换下来的中断重新装入IRR中

CPU从数据总线上拿到中断向量号止之后,用作中断向量表或者中断描述符表的索引,转到对应的中断处理程序执行。

设置中断的程序框架

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36;获取系统原80号向量的地址 es:bx

mov ax,3580H

int 21h

mov int80seg,es

mov int80off,bx

;设置新的向量

push ds ;保存ds

mov ax, seg new80

mov ds,ax

mov dx,offset new80

mov ax,2580h

int 21h

pop ds ;恢复ds

;设置IMR

in al,21h ;这是主片,从片使用0a1h

and al,0feh; 允许哪一位就设置哪一位为零。

out 21h,al;

;恢复原中断

;和设置一样,不在赘述

;中断程序的书写

;记得开中断

;记得发送EOI指令

new80 proc

sti ;开中断

;保护寄存器和中断程序处理

;EOI

mov al,20h

out 20h,al;主片

out 0a0h,al;从片

new80 endp中断程序驻留内存

1

2

3

4

5;dx中存放要驻留程序的长度(以16字节为单位)

add dx,15

shr dx,4

mov ax,3100h

int 21h

QUS

简答题

- 外设为什么不能和处理器之间相连?

- 微机的外设多种多样,工作原理、驱动方式、信息格式、工作速度千差万别,他们不可以直接和cpu相连接,必须通过中间电路(I/O)接口电路与系统连接。

- 计算机的两个功能部件、设备之间为什么一般需要数据缓冲?

- 数据缓冲用于匹配快速的处理器和相对慢速度额外设或者两个功能部件速度不匹配的数据交换。

- 什么时电路的命令字或者控制字?

- 处理器向特定的接口板芯片的吧相应端口写入特定的数据用于选择IO芯片的工作方式或者控制外设工作,该数据称为命令字或者控制字。

- 为什么说外部中断才是真正意义上的中断?

- 玩不终端是由处理器外部提出的中断请求引起的程序中断,对于处理器来说,外部中断时随机产生的,所以才是真正意义上的中断。

- IO接口电路的寄存器分类?

- 数据寄存器:保存处理器和外设之间交换的数据。

- 状态寄存器:保存外设当前的工作状态信息。

- 控制寄存器:保存处理器控制接口电路和外设进行操作的有关信息。处理器向控制寄存器写入信息选择接口电路的不同工作方式和与外设交换信息的数据格式。

- 简述主机和外设交换数据的几种方式。

- 无条件传送:最简单的数据传送,认为设备总是处于就绪状态。

- 程序查询方式:处理器查询外设的状态,在外设就绪的时候进行数据传输。

- 中断,外设就绪的时候通过请求引脚信号,主动向处理器提出交换数据的请求,处理器没有其他更加紧迫的任务就执行中断程序。

- DMA传送:DMA控制器可以接管总线,作为总线的主控设备,通过系统总线来控制存储器和外设直接进行数据交换。

- 以可屏蔽中断为例,说明一次完成的中断过程包括哪一些环节?

- 中断请求。

- 中断响应。

- 关中断。

- 断点保护

- 中断源识别

- 现场保护。

- 中断服务

- 回复现场。

- 开中断

- 中断返回。

编程题

编程

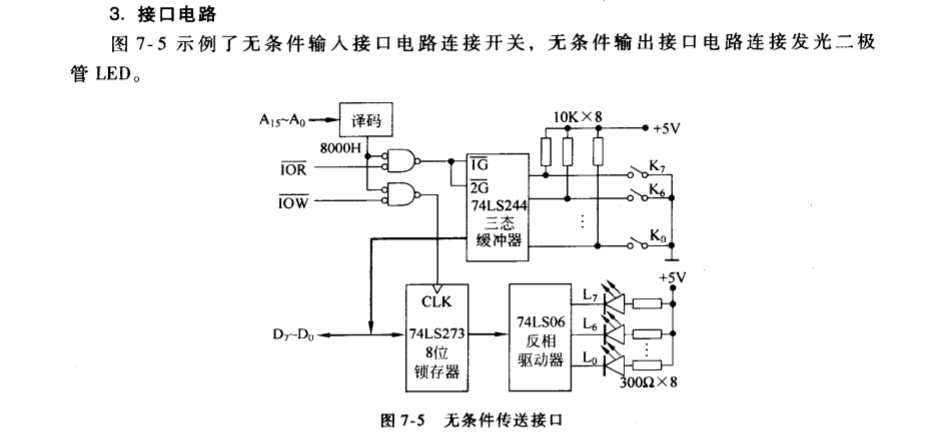

由图可知,开关时低电平有效(代表闭合),灯是高电平有效(代表亮),端口地址为80001

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28again:

mov dx,8000H

in al,dx

cmp al,11111110B ;k0单独按下

jz next0

cmp al,11111101B ;k1单独按下

jz next1

jmp again

next0:

;顺序点亮

mov cx,8

mov al,1

next11:

out dx,al

call delay

shl al,1

loop next11

jmp again

next1:

;倒序点亮

mov cx,8

mov al,10000000B

next11:

out dx,al

call delay

shr al,1

loop enxt11

jmp again编程

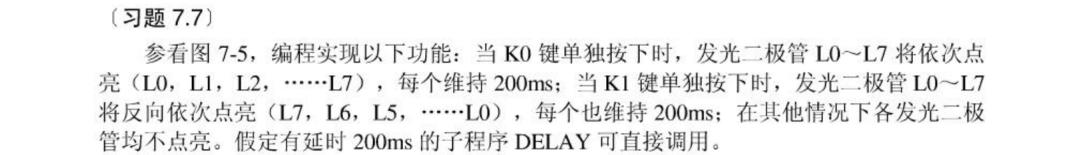

1

编程

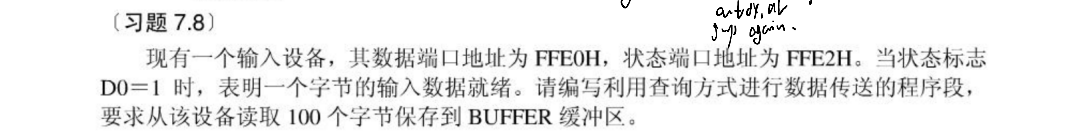

1

第八章 常用接口电路

8253/8254

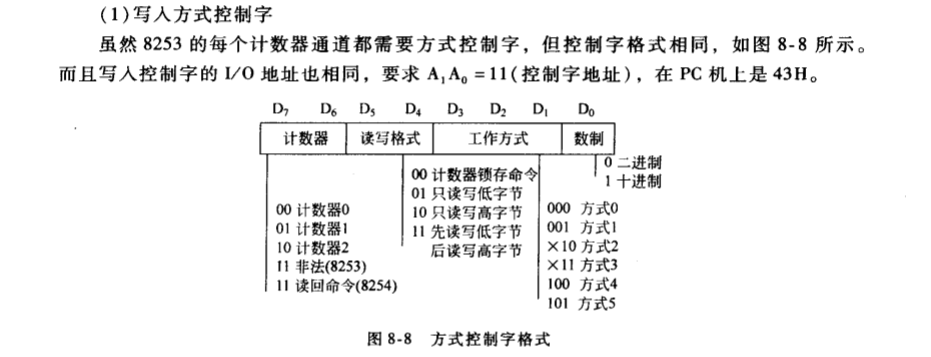

控制字

使用

- 定时中断 计数器0方式3 每秒产生计数器初值次的请求

1

2

3

4

5

6;计数器0,先低后高, 方式3,二进制

mov al,00110110b

out 43h,al ;方式控制字

mov al,0

out 40h,al ;低

out 40h,al ;高 - 定时刷新 使用计数器1方式2 产生可自动重新计时的中断进行刷新

1

2

3

4

5;计数器1,低字节,方式二,二进制

mov al,01010100b

out 43h,al

mov al,10

out 41h,al - 扬声器控制 计数器2 方式3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22ax=1193180/发声频率

;计数器2 先低后高 方式3 二进制

;写入计时器

push ax;

mov al,10110110b

out 43h,al

pop ax

out 42h,al

mov al,ah

out 42h,al

;发声

;读取61H端口,使得PB1 PB0=11

in al,61H

or al,00000011b;

out 61h,al

;闭声

;读取61H端口,使得PB1 PB0=00

in al,61H

and al,11111100b

out 61h,al

8255

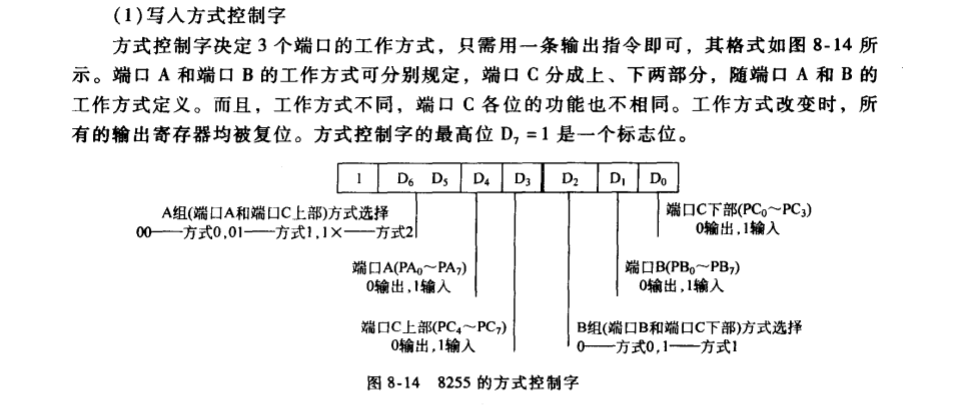

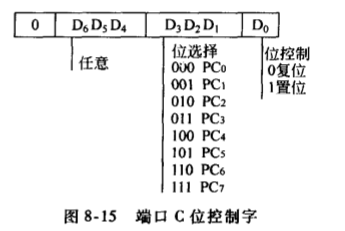

控制字

使用

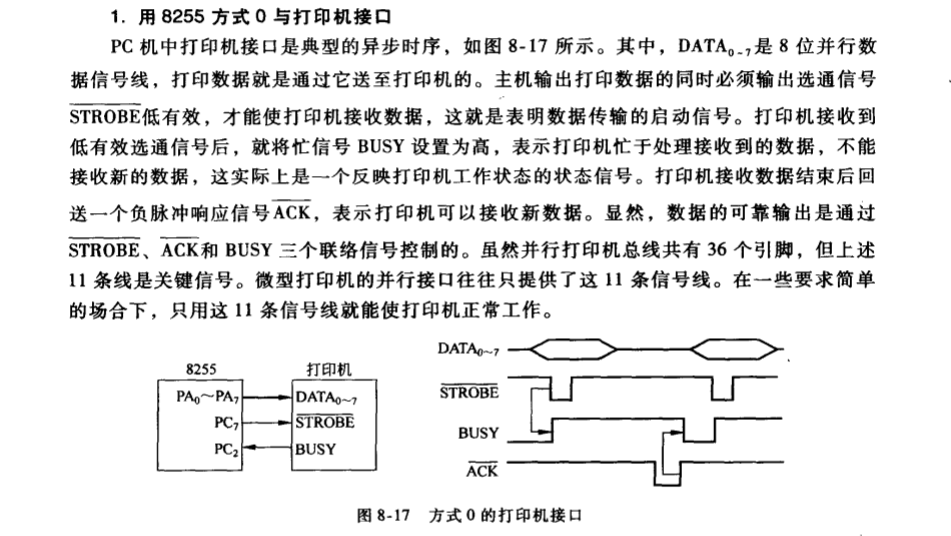

8255端口A使用方式0输出打印数据

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41;初始化程序

;端口A为方式0输出,端口C(PC7)上部分和A一样,下部分为输入(PC2)。

mov dx,0fffeh

mov ax,10000001b

out dx,al

;初始使得打印机不打印 即 STROBE 高电平

mov ax,00001111b

out dx,ax

;子程序 入口参数 AH为打印数据

printc proc

push ax

push dx

;查询PC2,看打印机是否忙 1为忙

wait:

mov dx,0fffch

in al,dx

and al,00000100b

jnz wait

;不忙,则输出数据

mov dx,0fff8h

mov al,ah

out dx,al

;使得STROBE=0 低电平有效,进行打印数据

mov dx,0fffeh

mov ax,00001110b

out dx,ax

;适当延时 维持低电平有效

nop

nop

;打印完了一个数据,使STROBE=1 无效

mov dx,0fffeh

mov ax,00001111b

out dx,ax

pop dx

pop ax

ret

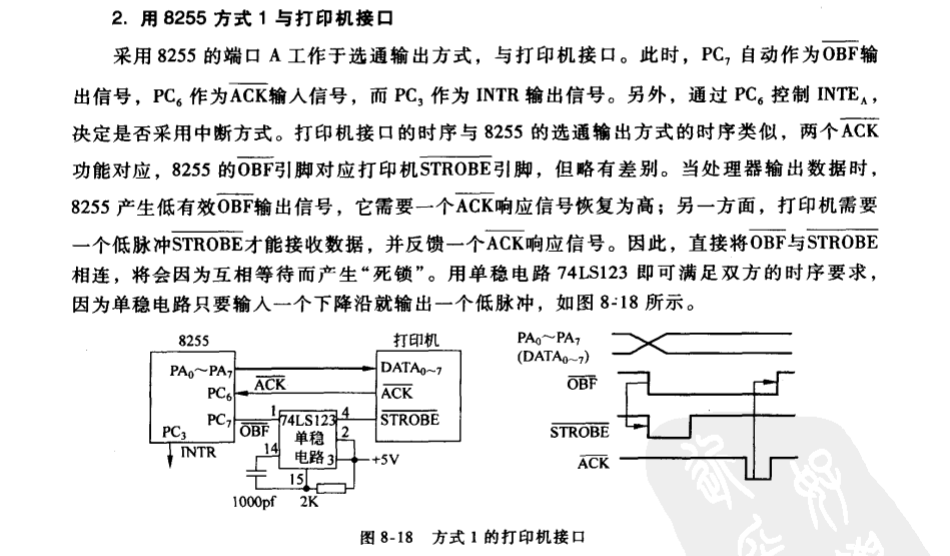

peintc endp8255端口A使用方式1输出打印数据

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33;初始化

mov dx,0fffeh

mov al, 10100000b ;不知道为什么 PC6也要为输出

out dx,al

;禁止中断 PC6=0

mov al,00001100b

out dx,al

;子程序 入口参数 AH为打印数据

printc proc

push ax

push dx

print:

;输出数据

mov dx,0fff8h

mov al,ah

out dx,al

;判断 PC7==0?

wait:

mov dx,0fffch

in al,dx

test al,10000000b

jz wait

;PC7==1 继续打印

jmp print

pop dx

pop ax

ret

peintc endp

数码管

- 数码管分为段码和位码。注意判断是共阴极还是共阳极,前者为低电平有效,后者为高电平有效。

数码管的使用

1 | include io.inc |

ADC

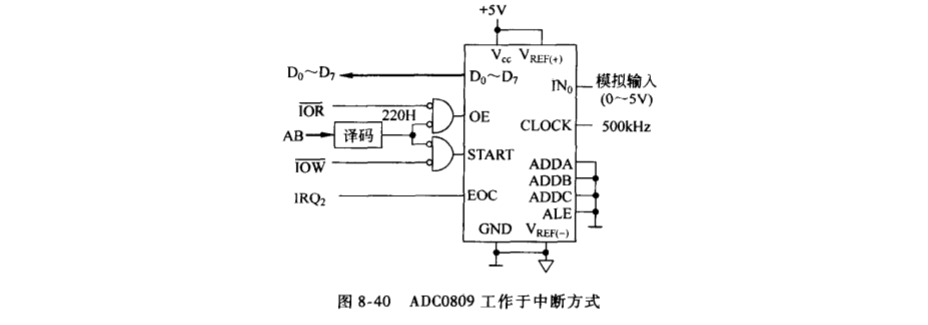

- 中断方式

1 | ;启动ADC |

- 查询方式

见实验代码

QUS

判断题

- 8255没有时钟信号,其工作方式1的数据传送采用异步传送。 √

- 调制解调器的信号调制是数字信号和模拟信号的转换,所以其转换原理与ADC或者DAC器件一样。 ×

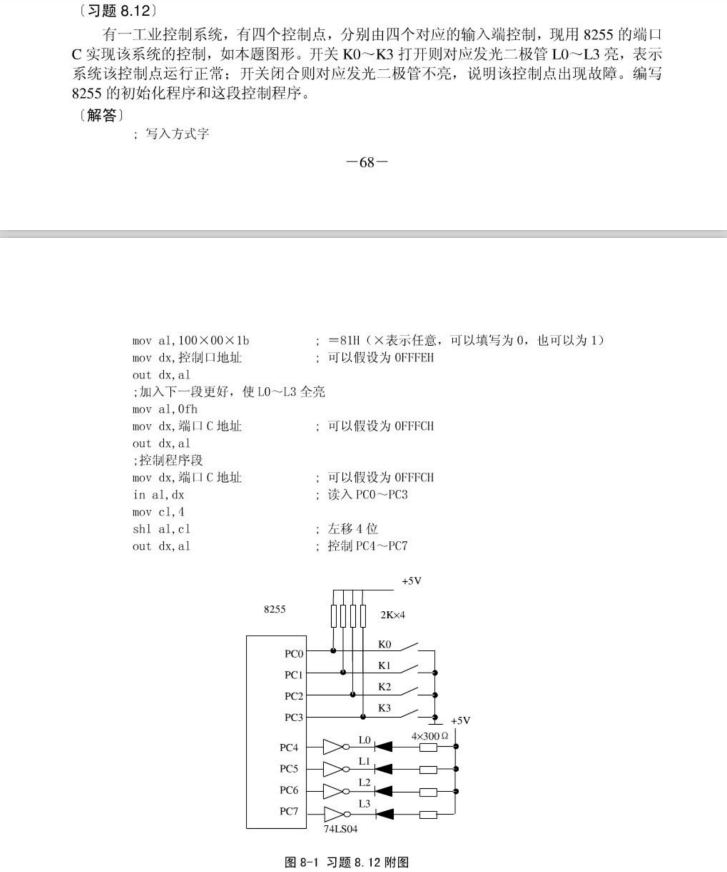

大题

偏移码

- 符号位取反的补码。

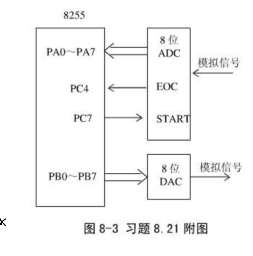

如图

如图